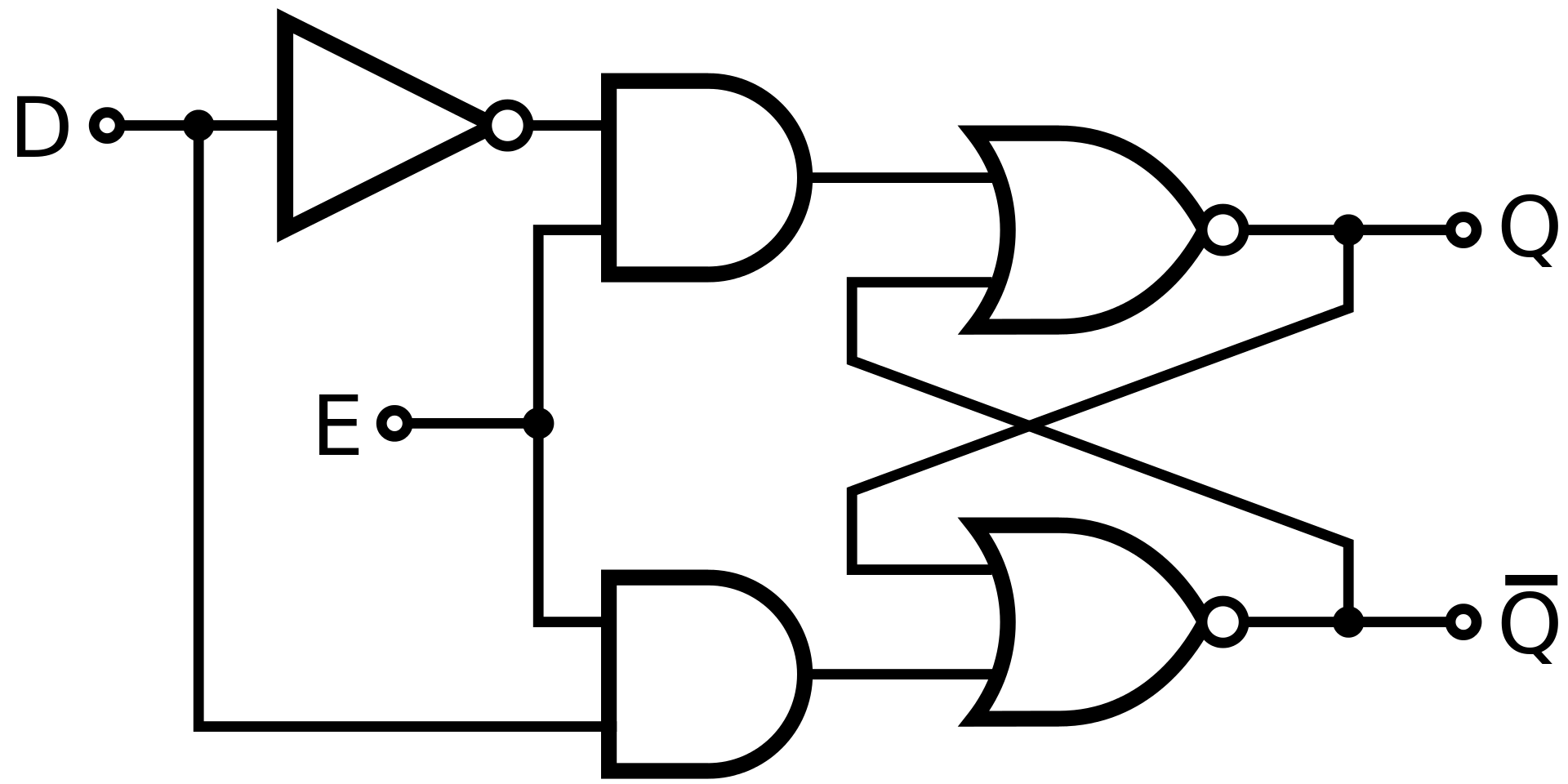

D latch는 논리회로로는 아래와 같은 회로도처럼 구현할 수 있다.

진리표의 경우 아래와 같으며, E는 CLK으로 취급할 수 있다. CLK로 취급하는 이유는 나중에 설명할 Master-Slave에서 E를 CLK로 사용하기 때문이다.

두 경우 전부 다 구현해보겠다.

module dlatch1( // nand only

input D, CLK,

output Q, Q_

);

wire R, S;

nand na0(S, D, CLK);

nand na1(R, S, CLK);

nand na2(Q, Q_, S);

nand na3(Q_, Q, R);

endmodule

module dlatch2( // and, or, not

input D, CLK,

output Q, Q_

);

wire R, S;

and a0(S, ~D, CLK);

and a1(R, D, CLK);

nor no2(Q, Q_, S);

nor no3(Q_, Q, R);

endmodule

베릴로그 표준은 nand와 nor을 ~&, ~|로 쓸 수 없다. 애초에 지원이 안된다;;

두 회로는 아주 정확히 똑같은 동작을 한다. Master-Slave 설계와 함께 비교해볼 것이다.

Master-Slave는 위에서 구현한 D latch를 두 개 연결한 것이다. 대신 Slave d latch에 입력되는 CLK 신호는 Master의 CLK 신호를 반전한 신호를 넣게 된다. 이렇게 연결하면 클락 신호의 edge(0->1 또는 1->0)에만 값을 저장하는 D flip flop이 된다.

위의 사진처럼 포트를 연결하면 D flip-flop이 완성된다. 코드를 참조한다. positive edge에 동작하도록 설계하였다.

module dff(

input D, clk,

output Q, Q_

);

wire Q_M, Q_M_;

dlatch1 MASTER(D, ~clk, Q_M, Q_M_);

dlatch2 SLAVE(Q_M, clk, Q, Q_);

endmodule

positive edge는 clk을 반대로 주면 된다.

이제 시뮬레이션으로 제대로 돌아가는지 확인해보자.

테스트 벤치를 첨부한다.

module tb();

reg D, CK;

wire Q1, Q1_;

wire Q2, Q2_;

wire Q3, Q3_;

dlatch1 TEST1(D, CK, Q1, Q1_);

dlatch2 TEST2(D, CK, Q2, Q2_);

dff TEST3(D, CK, Q3, Q3_);

initial begin

D <= 0;

CK <= 0;

#10

CK <= 1;

#10

D <= 1;

#10

CK <= 0;

#10

D <= 0;

#10

D <= 1;

#10

CK <= 1;

#10

D <= 0;

#10

CK <= 0;

#10

CK <= 1;

#10

D <= 1;

#10

CK <= 0;

#10

D <= 0;

#10

$finish;

end

endmodule

Q1과 Q2는 CK가 1일 때, Q3는 CK의 positive edge(0->1)에 값을 저장한다.

이렇게 설계하긴 했지만 실제로 D flip flop은 따로 MOSFET으로 설계한다. 위의 예시는 논리회로 배우는 학생들을 위해 일부러 쉽게 구현한 예시일 뿐이다.

레지스터 변수는 따로 특별히 다른 flip flop을 쓴다고 설정 안 하면 D flip flop으로 합성을 하게 된다. 이때 위의 예시 같은 걸 쓰면 면적이 너무 커진다. 그래서 보통 D flip flop은 따로 MOSFET으로 모델링을 해둔다.

혹시나 궁금할까봐 회로도를 첨부한다.

이 글은 위키피디아를 참조하여 작성되었습니다.

https://en.wikipedia.org/wiki/Flip-flop_(electronics)

'Verilog HDL 설계' 카테고리의 다른 글

| BCD to 7 segment (0) | 2021.04.19 |

|---|---|

| 간단한 Deinterleaver (0) | 2021.04.18 |

| 8bit Binary to BCD (0) | 2021.04.14 |

| 코드 작성을 위한 몇가지 팁(1) (3) | 2021.04.14 |

| MUX (0) | 2021.04.13 |