코딩하다보면 비슷한 회로지만 비트수가 다른 회로를 설계하는 경우가 있다.

이걸 편하게 해주는 기능이 베릴로그에도 있다.

파라미터를 모듈과 함께 선언해주는 방법인데, 이걸 잘 활용하면 코딩 시간을 좀 줄일 수도 있다.

간단하게 카운터로 예시를 살펴보자.

module counter

#(parameter param1 = 4,

parameter param2 = 14)

(

output [param1-1:0] count,

input clk, rst

);

reg [3:0] cntreg;

always @ (posedge clk) begin

if (rst) begin

cntreg <= 4'b0;

end

else begin

if (cntreg == param2) begin

cntreg <= 4'b0;

end

else begin

cntreg <= cntreg + 4'b1;

end

end

end

assign count = cntreg;

endmodule

기본적으로 설정한 param2에 의해 0~14까지 카운트하는 카운터를 만들었다.

또한 param1에 의해 비트수가 결정된다.

따라서 해당 카운터 모듈은 원하는 비트, 원하는 카운터값을 자유자재로 설정할 수 있다.

이제 이걸 어떻게 이용하는지 살펴보자

module example(

output [3:0] cnt,

input clk, rst,

input [1:0] sel

);

wire [3:0] cnt0, cnt1, cnt2, cnt3;

wire [3:0] tmp0, tmp1, tmp2;

counter #(.param1(4), .param2(9)) counter0(.count(cnt0), .clk(clk), .rst(rst));

counter #(.param1(4), .param2(10)) counter1(.count(cnt1), .clk(clk), .rst(rst));

counter #(.param1(4), .param2(11)) counter2(.count(cnt2), .clk(clk), .rst(rst));

counter #(.param1(4), .param2(12)) counter3(.count(cnt3), .clk(clk), .rst(rst));

assign tmp0 = sel[0] ? cnt1 : cnt0;

assign tmp1 = sel[0] ? cnt3 : cnt2;

assign tmp2 = sel[1] ? tmp1 : tmp0;

assign cnt = tmp2;

endmodule

이것까지 html에서 지원하지는 않는듯하다.... 원래는 아래처럼 표시된다.

모듈이름 #(파라미터값1, 파라미터값2, ...) 모듈인스턴스(포트1, 포트2, ...)

처럼 선언하면 된다.

당연하지만 .param1 대신 순서대로 값을 넣어도 똑같이 동작한다.

예) counter #(4, 9) counter0(cnt0, clk, rst);

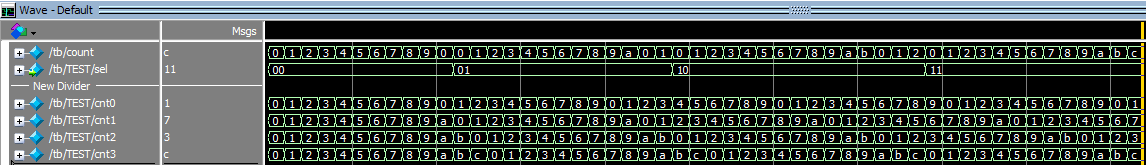

해당 모듈은 sel 값에 따라 4개의 카운터 값 중 하나를 출력한다.

카운터는 순서대로 9, 10, 11, 12까지 카운트하는 회로다.

테스트벤치

`timescale 1ns/1ps

module tb();

reg clk, rst;

reg [1:0] sel;

wire [3:0] count;

initial begin

clk <= 1;

rst <= 1;

sel <= 2'b0;

#10

rst <= 0;

#100

sel <= 2'd1;

#130

sel <= 2'd2;

#150

sel <= 2'd3;

#130

$finish;

end

example TEST(count, clk, rst, sel);

always #5 clk <= ~clk;

endmodule해당 테스트벤치로 시뮬레이션하면 다음과 같은 파형을 확인할 수 있다.

의도한 것처럼 각 카운터의 동작을 확인할 수 있었다.

'Verilog HDL 설계' 카테고리의 다른 글

| 덧셈과 뺄셈, 그리고 sign extension (0) | 2022.06.02 |

|---|---|

| include의 필요성 및 사용법 (0) | 2022.04.12 |

| Simple Finite State Machine implementation (0) | 2021.04.29 |

| 테스트벤치 작성 예시 (0) | 2021.04.25 |

| Countdown control & display (0) | 2021.04.23 |