Verilog 시뮬레이션 툴들은 다양하다.

Altera 사의 modelsim, Xilinx 사의 vivado, Cadence 사의 Xcelium(ncverilog), Synopsys 사의 vcs가 대표적이다.

학부생들이 주로 사용하는 툴은 modelsim과 vivado이다.

FPGA를 사용하기 위해 쓰는 경우가 많다.

modelsim은 Altera 사의 Quartus라는 툴에 대응되는 FPGA 보드를 사용하기 위해 사용된다.

vivado는 Xilinx 사에서 지원하는 FPGA 보드를 사용하기 위해 사용된다.

Icarus Verilog는 라이센스 걱정없이 자유롭게 Verilog 시뮬레이션을 수행할 수 있으며, 터미널 환경에서의 컴파일 환경을 경험하기에 좋은 툴이다.

특히 Include를 직접 사용하기에 정말 좋은 툴이다.

Include는 modelsim, vivado에서도 사용될 수 있으나 두 툴에서는 굳이 쓸 필요가 없기 때문에 자주 쓰이지는 않는다.

하지만 Icarus Verilog는 Include를 사용하지 않으면 실행 명령어가 쓸데없이 길어지는 단점이 있다.

Icarus Verilog를 설치하는 방법 중에 하나는 exe 파일을 사용해 설치하는 것이다.

Icarus Verilog for Windows

bleyer.org

해당 사이트를 통해 최신 버전을 다운받을 수 있다.

#팁1

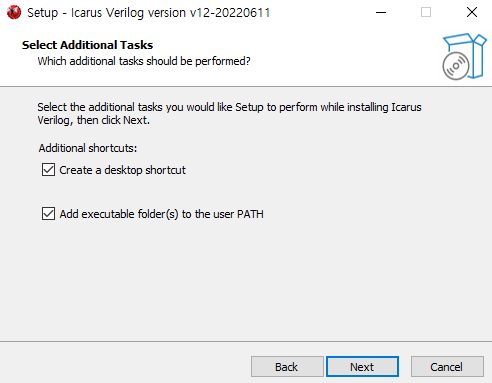

설치 시 신경써야할 부분은 desktop(바탕화면) shortcut과 Add Path인데, 해당 항목은 자동으로 체크되어 있지 않다.

다른 블로그에서는 따로 설정하는 것처럼 설명을 해뒀는데, Add Path 옵션을 체크해두면 수작업으로 Path를 추가하지 않아도 된다.

해당 단계에서 체크해주면 된다. 바탕화면 바로가기는 굳이 안해도 상관없다.

VS code에서는 자체적으로 터미널을 지원하기 때문에 편리하게 사용할 수 있다.

Icarus Verilog를 실행하기 위해서는 테스트벤치에 해당 코드를 추가하면 된다.

`timescale 1ns/1ps

module tb_dct_top();

dct_top TEST(data_out, data_in, clk, rst, enb);

// skip main code

// icarus verilog part

initial begin

$dumpfile("test_out.vcd"); // any file name possible

$dumpvars(0, TEST); // instance name required

end

endmodule

$dumpfile 명령어는 gtkwave에서 사용되는 데이터 파형을 만들기 위해 사용되며, 아무 이름이나 이름지어도 상관없다.

$dumpvars는 아래와 같은 구조인데, level은 하위 몇 레벨까지의 데이터를 덤프 파일로 만들지 결정하며, 모듈명은 덤프 파일로 만들어지는 top level module을 나타낸다.

$dumpvars( <level>, <module_or_variable> )

해당 코드를 작성한 후, 터미널에서 아래와 같은 명령어를 입력하면(dct code를 예시로 들었다) 컴파일된 파일이 만들어진다.

iverilog -o AnyFileName tb_dct_top.v dct_top.v dct_1d.v dct_2d.v tp_mem.v

출력으로 아무 이름의 파일을 만든 후, vvp 명령어를 통해 시뮬레이션을 수행하면 덤프 파일을 만든다.

vvp AnyFileName

이제 dump file인 test_out.vcd 파일이 생성됐을 것이다. 데이터를 보기 위해 gtkwave를 실행시킨다.

gtkwave test_out.vcd

이후 데이터를 보는 과정은 다른 툴과 비슷하기 때문에 생략하겠다.

모든 베릴로그 파일을 적었기 때문에 iverilog 명령어가 매우 지저분한 것을 알 수 있다.

#팁2

include를 사용하면 단일 파일 이름만 적어서 시뮬레이션이 가능해진다.

`include "./dct_top.v"

module tb_dct_top()

dct_top TEST(...)

위와 같이 코드를 작성하면 dct_top.v 파일이 tb_dct_top.v에서 불러와진다.

이 코드를 하위 모듈에도 적용하면 모든 파일을 한 파일에서 불러올 수 있다.

예시는 깃허브에 추가해뒀는데, RISC-V repositorie에는 추후에 추가할 예정이다.

#팁3

터미널의 기능 중에 하나는 탭 키를 사용해 자동완성을 해준다는 것인데, 이걸 iverilog에서도 적용하면 시뮬레이션이 좀더 편해진다.

깃허브에서 테스트벤치 파일들을 보면 전부 "tb_"가 붙는것을 알 수 있는데, 이는 탭 키의 자동완성 기능을 사용하기 위함이다.

사용법은 "iverilog -o AnyFileName tb_" 까지 적은 후 탭 키를 사용하여 테스트벤치 파일을 선택하는 것이다.

탭 키를 사용하면 테스트벤치 파일 이름을 자동완성하게 되어 명령어를 끝까지 작성하지 않아도 된다.

여기서 주의할 점은 프로젝트마다 새 폴더에 저장을 해둬야 위 방법을 사용하기 쉽다는 것이다.

만약 한 폴더에 여러 프로젝트 파일을 저장하게 된다면 테스트벤치 파일이 많아져서 탭 키를 사용해도 원하는 테스트벤치 파일을 찾기 힘들어지게 된다.

'Verilog HDL 설계' 카테고리의 다른 글

| Tree Multiplier(16bit Dadda Multiplier) (0) | 2023.02.24 |

|---|---|

| 4bit/16bit Carry Lookahead Adder 설계 (0) | 2023.02.22 |

| Single Cycle RISC-V 32I 프로세서 설계 (6) | 2022.07.14 |

| Deinterleaver 심화 - mod 1536 (0) | 2022.07.07 |

| Discrete Cosine Transform 구현 (2) | 2022.06.30 |