Clock frequency divider는 클락 주파수(clock frequency)를 나누는, 즉 기본 클락 주기의 2, 3, 4... 등의 배수의 클락을 만들어내는 회로다. 이미지 출처는 아래에 적어뒀다.

https://theorycircuit.com/frequency-divider-circuit/

주파수를 나누기 위해서는 카운터가 필요하다. 아래와 같이 구현이 가능하다.

module clk_divide(

input clk, rst,

output reg clk_2, clk_4, clk_6

);

reg [1:0] count;

reg [1:0] count2;

reg enb;

// assign clk_out = count[3];

always @ (posedge clk) begin

if (rst) begin

count <= 2'b0;

count2 <= 2'b0;

clk_2 <= 1'b0;

clk_4 <= 1'b0;

clk_6 <= 1'b0;

end

else begin

count <= count + 2'b1;

clk_2 <= ~clk_2;

if (count[0]) begin

clk_4 <= ~clk_4;

end

if (count2 == 2'd2) begin

count2 <= 2'b0;

clk_6 <= ~clk_6;

end

else begin

count2 <= count2 + 2'b1;

end

end

end

endmodule

2로 나누는 경우는 그렇게 어려운 것이 아니다. 그냥 posedge clk 마다 반전되도록 하면 된다.

4로 나누는 경우는 카운터를 사용해서 첫번째 비트가 1일 경우 반전되도록 하면 구현이 된다.

6으로 나누는 경우는 0~2까지의 카운터를 사용해 주기의 절반마다 반전되도록 하여 구현하였다.

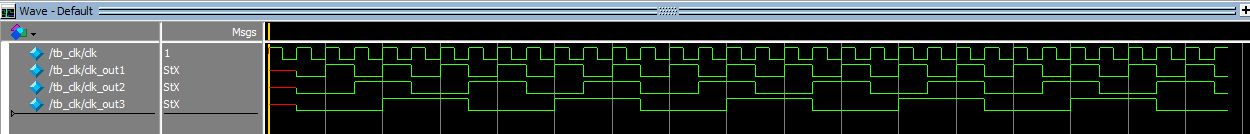

테스트벤치를 아래와 같이 작성하고 시뮬레이션을 돌려봤다.

module tb_clk();

reg clk, rst;

wire clk_out1, clk_out2, clk_out3;

initial begin

clk <= 1;

rst <= 0;

#5

rst <= 1;

#10

rst <= 0;

#320

$finish;

end

always #5 clk <= ~clk;

clk_divide TEST(clk, rst, clk_out1, clk_out2, clk_out3);

endmodule

'Verilog HDL 설계' 카테고리의 다른 글

| 8bit Binary to BCD (0) | 2021.04.14 |

|---|---|

| 코드 작성을 위한 몇가지 팁(1) (3) | 2021.04.14 |

| MUX (0) | 2021.04.13 |

| Counter (2) | 2021.04.11 |

| Verilog HDL 문법 소개 (0) | 2021.04.11 |